# OUTLINE

- 1. Introduction and Importance of IC Design Verification

- 2. Lecture

- Functional Verification of DCLS Feature of RISC-V

- 3. Practical Demonstration

- Simulating the open-source SweRV EH1 core using RISC-V Tool chain + Synopsys VCS

Presented by: National Electronics Complex of Pakistan (NECOP)

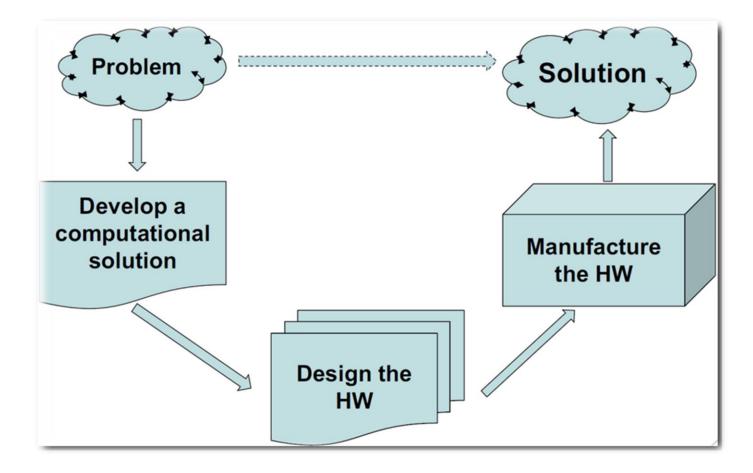

# INTRODUCTION AND IMPORTANCE OF IC DESIGN VERIFICATION

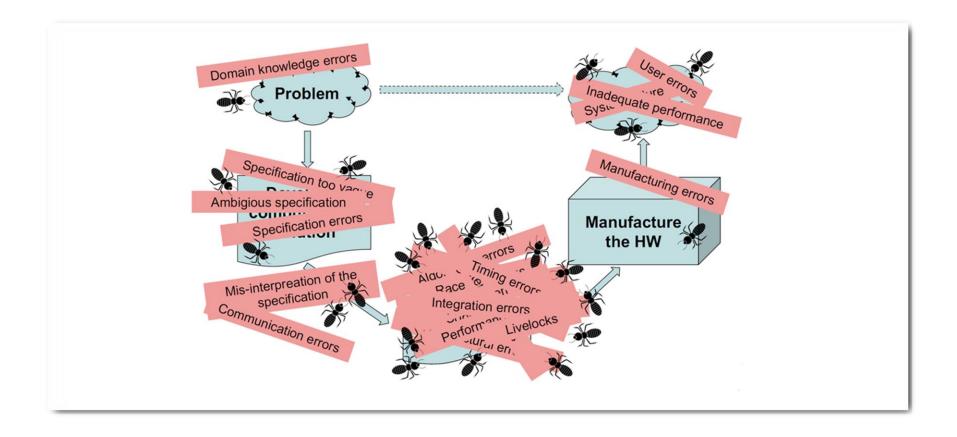

# WHAT IS DESIGN VERIFICATION?

Design verification is the process used to gain confidence in the correctness of a design w.r.t. the requirements & specifications.

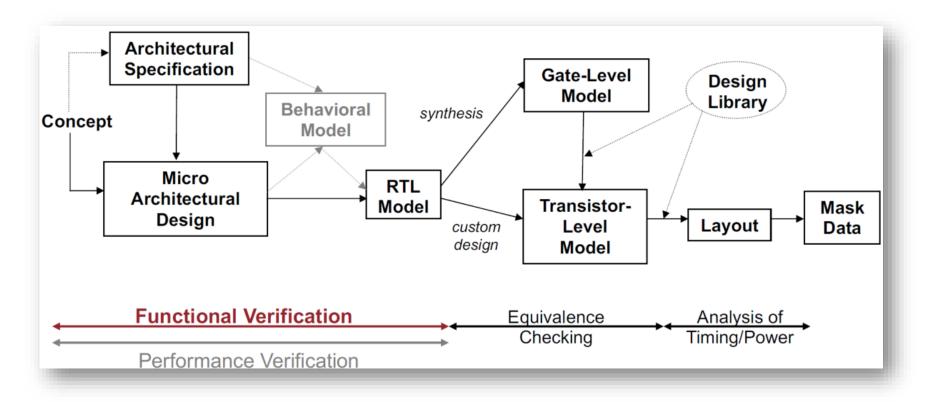

# **VERIFICATION IN THE IC DESIGN PROCESS**

Functional verification aims to demonstrate that the functional intent of a design is preserved in its implementation.

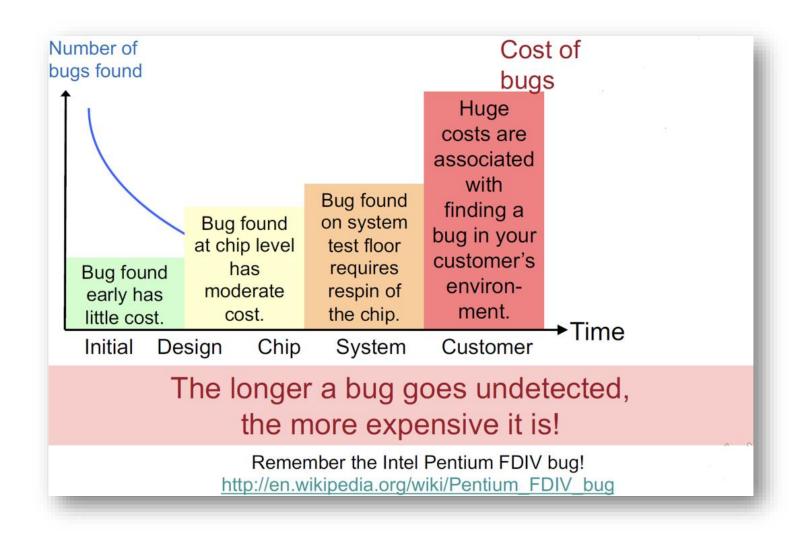

# **COST OF BUGS OVER TIME**

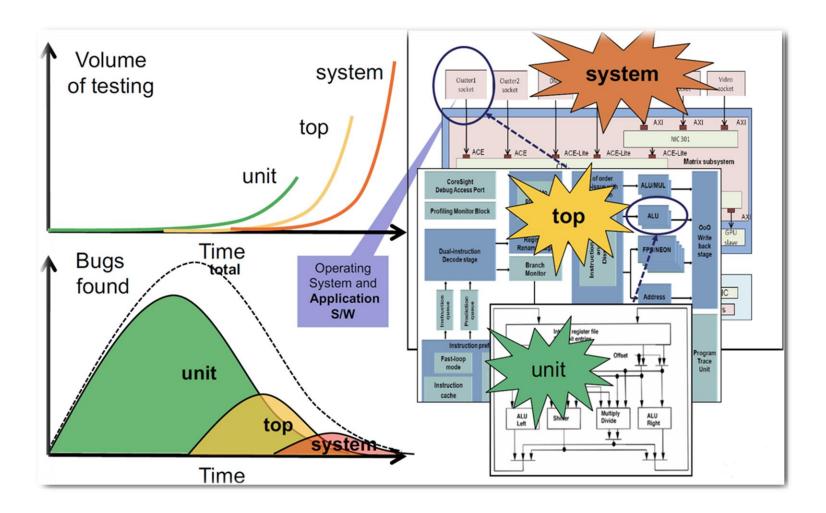

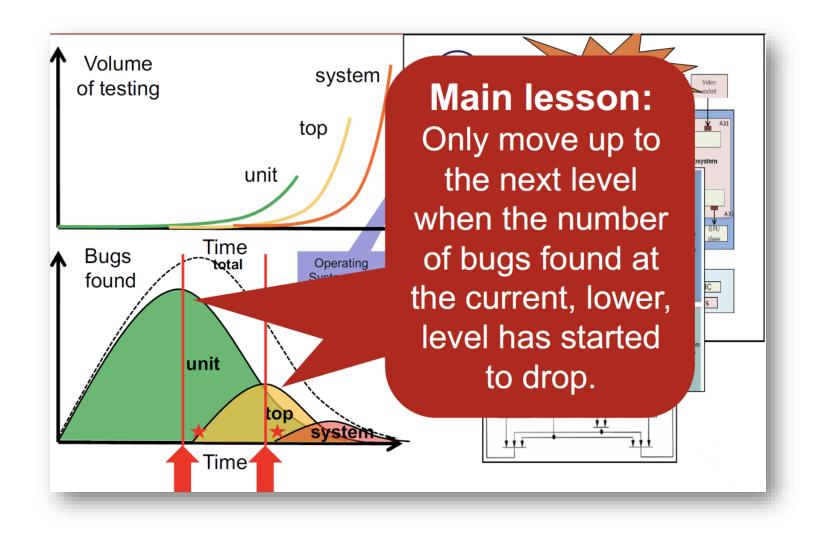

# VERIFICATION AT DIFFERENT DESIGN LEVELS

# VERIFICATION AT DIFFERENT DESIGN LEVELS

Verification is the single biggest lever to affect the triple constraints:

### Quality

- i. A high-quality track record preserves revenue and reputation.

- ii. Ideally a team can establish a "right-first-time" track record.

### • Cost

- i. Fewer revisions through the fabrication/development process means lower costs.

- ii. Re-spinning a chip costs hundreds and thousands of dollars.

### Timing/Schedule

- i. Fewer revisions through the fabrication/development process means faster time-to-market.

- ii. Re-spinning a chips costs 6-8 weeks at least.

# **ROLE OF VERIFICATION IN IC DESIGN**

- Engineers need to balance the conflict of interest:

- Tight time-to-market constraints vs. increasing design complexity

- Aim: "Right-first-time" design, "correct-by-construction"

- More and more time-consumed to obtain acceptable level of confidence in correctness of design!

- Design time << Verification time</li>

- Upto 70% of design effort can go into verification

- Remember: Verification does not create value! But it preserves revenue and reputation!

- In some cases, verification engineers out number designers 2:1

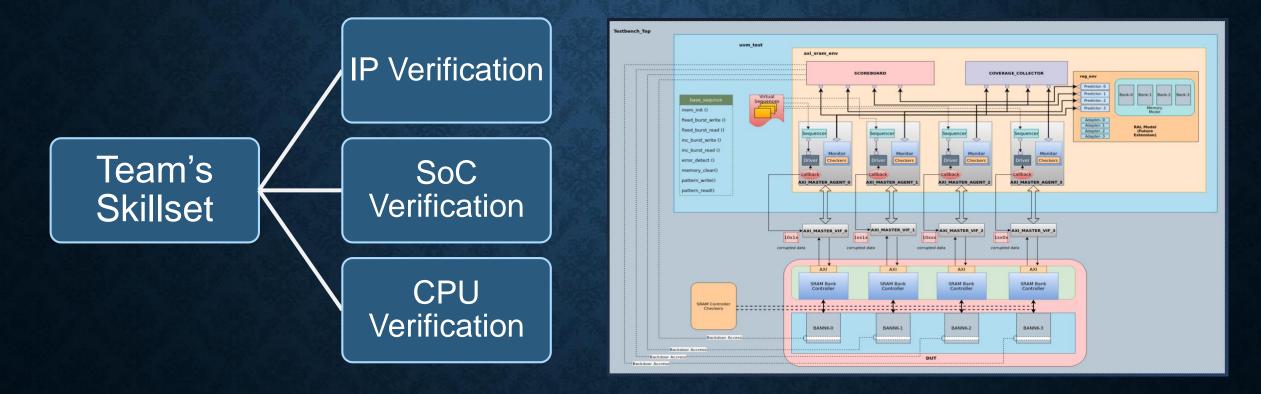

# **DESIGN VERIFICATION TEAM @ NECOP**

- Established in 2022

- Functional verification of RTL designs provided by the design teams

# **DESIGN VERIFICATION TEAM @ NECOP**

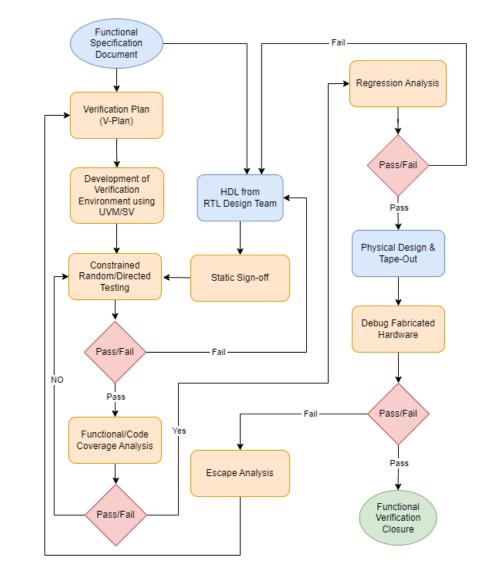

# **NECOP DV TEAM WORKING FLOW**

### Verification Tools:

### 1. Synopsys

- SpyGlass

- Verdi Debug

- VCS

- VC Execution Manager

### 2. Cadence

- Jasper Gold

- Xcelium

- V-Manager

### 3. Mentor Graphics

- HDL Designer

- QuestaSim

# **VERIFICATION LANGUAGES**

### Programming Languages

- Verilog/System Verilog

- UVM Methodology

- C/C++

- SystemC

- Scripting Languages

- Makefile

- Python

- Bash

- Tcl

# FVDCLS

Functional Verification of RISCV based Dual-Core Lockstep Feature using Fault Injection Mechanism

# Welcome to the open era of computing.

### RISC-V°

## RISC-V is the free and open Instruction Set Architecture...

- ... Driven through open collaboration

- ... Enabling freedom of design across all domains and industries

- ... Cementing the strategic foundation of semiconductors

# Disruptive **Technology**

### **Barriers**

Complexity

Design freedom

License and Royalty fees

Design ecosystem

Software ecosystem

## Legacy ISA

1500+ base instructions Incremental ISA

\$\$\$ – Limited

\$\$\$

Moderate

Extensive

### **RISC-V ISA**

47 base instructions Modular ISA

Free – Unlimited

Free

Growing rapidly. Numerous extensions, open and proprietary cores

Growing rapidly

# Industry innovation on RISC-V

# Complexity

Hardware – RV32 –

**Proof of Concept SoCs**

Minion processors for

power management,

communications, ...

**Software**

Bare metal software

2017 - 2018

#### Hardware

– RV32, privilege modes, interrupts –

IoT SoCs Microcontrollers

> **Software** RTOS Firmware

2019 - 2020

#### Hardware

– RV64, multi-heart

CPUs, vectors,

bit manipulation,

hypervisors, debug mode –

Al SoCs Application processors

Software Linux Drivers Al Compilers

2021

RISC-V°

Hardware

ISA Definition

**Test Chips**

**Software**

Tests

2010 - 2016

# **ISA Discussion**

The base integer ISA is named "I" (prefixed by RV32 or RV64 depending on integer register width), and contains integer computational instructions, integer loads, integer stores, and control-flow instructions;

Integer multiplication and division extension is named "M", and adds instructions to multiply and divide values held in the integer registers;

Standard single-precision floating-point extension is denoted by "F", adds floating-point registers, single-precision computational instructions, and single-precision loads and stores;

# **ISA Discussion**

| 31 30 25                                            | 24 21                    | 20                       | 19  | 15  14  | 12    | 11 8                 | 7                        | 6    | 0          |

|-----------------------------------------------------|--------------------------|--------------------------|-----|---------|-------|----------------------|--------------------------|------|------------|

| funct7                                              | rsź                      | 2                        | rs1 | fı      | unct3 | rc                   | 1                        | opco | de R-type  |

|                                                     |                          |                          |     |         |       |                      |                          |      |            |

| imm[1]                                              | 1:0]                     |                          | rs1 | fı      | unct3 | rc                   | 1                        | opco | ode I-type |

|                                                     |                          |                          | _   |         |       |                      |                          |      |            |

| imm[11:5]                                           | $rs^2$                   | 2                        | rs1 | fı      | unct3 | $\operatorname{imm}$ | [4:0]                    | opco | ode S-type |

|                                                     |                          |                          |     |         |       |                      |                          |      |            |

| $\operatorname{imm}[12]   \operatorname{imm}[10:5]$ | rs2                      | 2                        | rs1 | fı      | unct3 | imm[4:1]             | $\operatorname{imm}[11]$ | opco | ode B-type |

|                                                     |                          |                          |     |         |       |                      |                          |      |            |

|                                                     | $\operatorname{imm}[31]$ | :12]                     |     |         |       | rc                   | 1                        | opco | ode U-type |

|                                                     |                          |                          |     |         |       |                      |                          |      |            |

| $\operatorname{imm}[20]$ $\operatorname{imm}[1]$    | 0:1]                     | $\operatorname{imm}[11]$ | imn | n[19:1: | 2]    | rc                   | 1                        | opco | ode J-type |

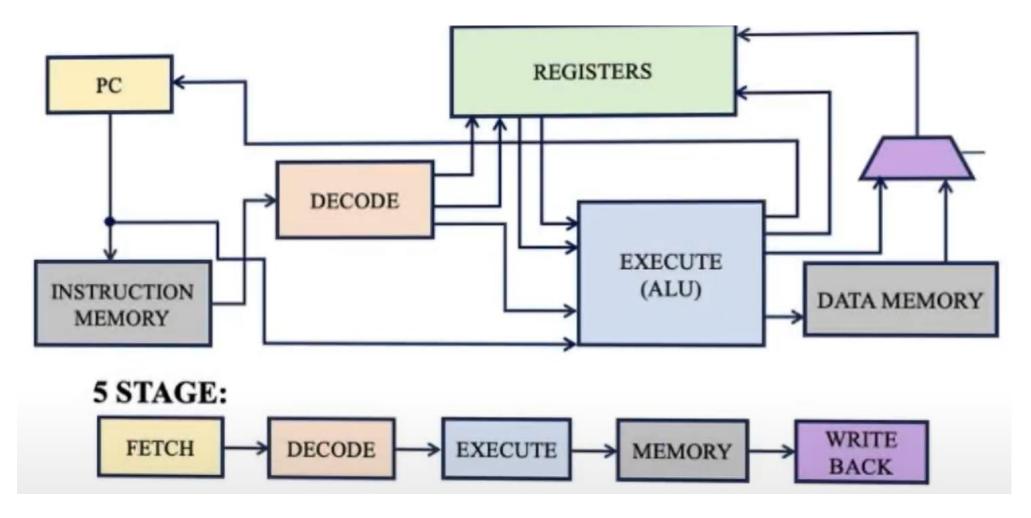

# **Classical 5-Stage Pipelining in RISC-V**

# **RISC-V Load/Store Architecture**

```

R1 <- [1]

R2 <- [2]

R3 <- [3]

```

In the code above, we are performing three load types. In line one, we are storing the address 1 to R1, line 2, we are storing address of 2 to R2 and finally in line 3, we are storing the address 3 to R3.

The RISC Pipeline will look something like this:

| Code      | Instruction line | Step 1 | Step 2 | Step 3  | Step 4  | Step 5  | Step 6 | Step 7 |

|-----------|------------------|--------|--------|---------|---------|---------|--------|--------|

| R1 <- [1] | 1                | Fetch  | Decode | Execute | Memory  | Write   |        |        |

| R2 <- [2] | 2                |        | Fetch  | Decode  | Execute | Memory  | Write  |        |

| R3 <- [3] | 3                |        |        | Fetch   | Decode  | Execute | Memory | Write  |

# **RISC-V** based General Processor

# **MOTIVATION OF DCLS CORE**

- Dual-core lockstep cores are used to

- i. Enhance fault tolerance,

- ii. Improve reliability, and

- iii. Meet the stringent safety requirements of critical applications.

- They provide a robust and proven approach to building high-reliability computing systems that can withstand hardware faults and environmental challenges.

# **SOURCES OF FAILURES**

### • Radiational Issues in ICs (SEUs)

• Memory: There is an accidental trigger that changes the memory state in the system. Common scenarios include a hit by a radiation particle, interference from RF transmitter

### • Single Event Latchup (SEL)

• Short-circuits between the power signal and the ground

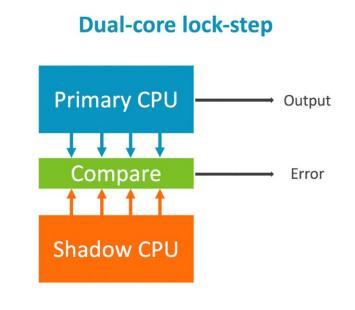

# WHAT IS DUAL-CORE LOCKSTEP (DCLS)?

- Dual-core lockstep (DCLS) is a redundancy technique for high-reliability computing used in safety-critical systems like aerospace, automotive, and industrial control systems.

- Both core's internal states & outputs are compared at each clock cycle.

- Any divergence or mismatch between core's states is indicated as an error in the system.

# **GENERIC DCLS BLOCK DIAGRAM**

# CHECKPOINT AND ROLLBACK METHODOLOGY

- The checkpoint is an operation that saves a consistent state of the processor in the memory

- The rollback recovers the system from an error by restoring that previous state

- When the Checker detects a mismatch in the CPU's data output the interrupt is launched to perform a rollback.

# COMMON MODE FAILURES

- DCLS cannot detect potential failures that can occur at the same point in both cores since the failures do not cause any difference between their outputs.

- These failures are referred to as common mode failures, which cause false match in the DCLS system.

# **TEMPORAL DIVERSITY**

- A common approach to this is delaying the redundant core for few cycles by inserting shift registers into the inputs.

- With a temporal diversity of even a few cycles, it is less likely that an erroneous trigger occurs at the same point of two cores.

- Note that this approach requires resynchronization of outputs from two cores before comparisons.

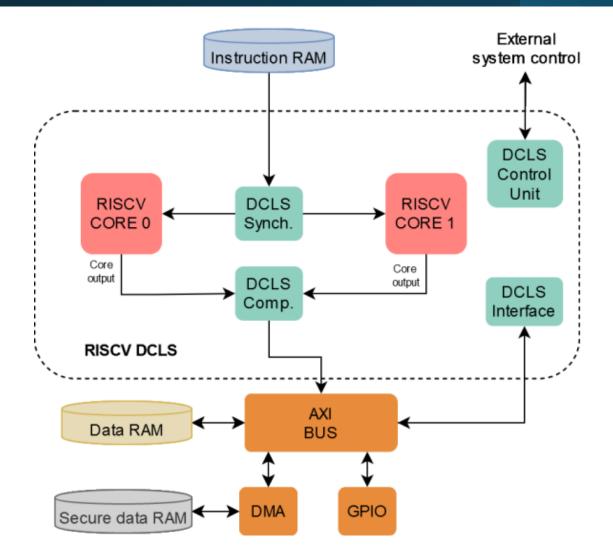

# **REFERENCE DESIGN**

- An Open-Source SweRV-Core with Integrated DCLS Feature

- RV32-IMF architecture where "I" stands for Integer, "M" Multiplication & "F" for floating point

- <u>GitHub chipsalliance/Cores-VeeR-EH1: VeeR EH1</u>

<u>core</u>

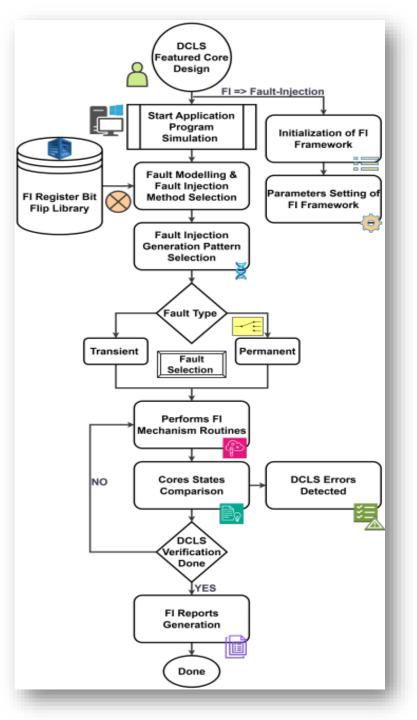

# DIFFERENT FAULT INJECTION (FI) TECHNIQUES

Hardware and software-based techniques

This work focus on software-based FI techniques

• Software-based techniques are categorized based on the time of fault-injection, i.e, compile-time, and run-time

Code Modification/Insertion

RTL of design under verification (DUV) is altered during run-time.

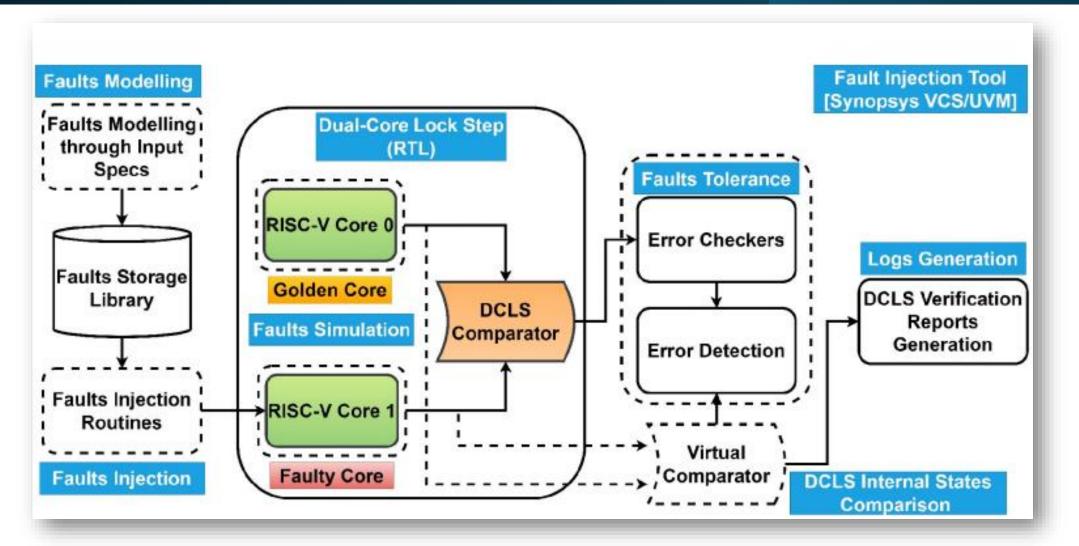

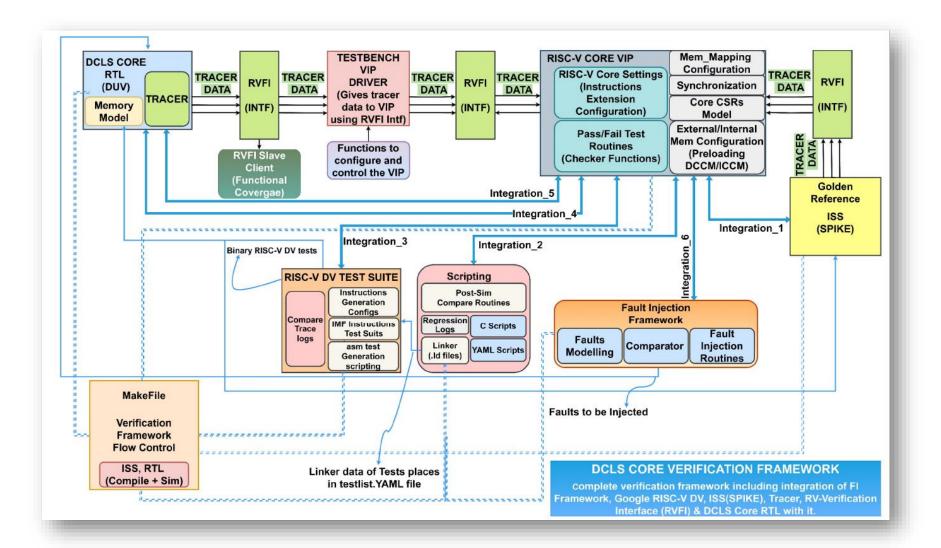

#### **PROPOSED FI FRAMEWORK**

#### FLOW DIAGRAM

38

### **Faults Modeling**

The process of describing and characterizing the types, locations, and behaviors of faults that might arise in SoCs is known as fault modelling.

In the proposed FI framework, faults are modelled using UVM-macros.

The UVM-macros allows backdoor access to DUV internal registers.

Hundred different DCLS internal state signals are accessed in the fault model, for customizing or flipping their existing stored data.

39

The UVM macros used for faults modelling are: (i) uvm-hdl-deposit, (ii) uvm-hdl-force, (iii) uvm-hdl-force-time, (iv) uvm-hdl-release and (v) uvm-hdl-read.

#### USED APPLICATION CASES

- The applications used to test DCLS functionality is an opensource Test-Suite known as "Google RISC-V DV".

- <u>GitHub chipsalliance/riscv-dv: Random instruction</u> generator for RISC-V processor verification.

## **Faults Simulation**

Application cases in the form of Google RISC-V DV testsuite are applied to the DUV.

Faults are induced during each application test case simulation.

Simultaneously, the FI routines are also applied to the DUV.

The resulting fault's latency, propagation and severity levels are then analyzed using simulation waveforms data.

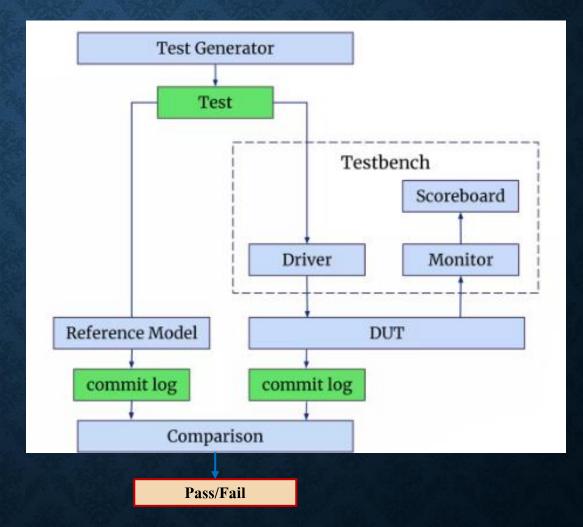

#### **UVM-BASED TESTBENCH**

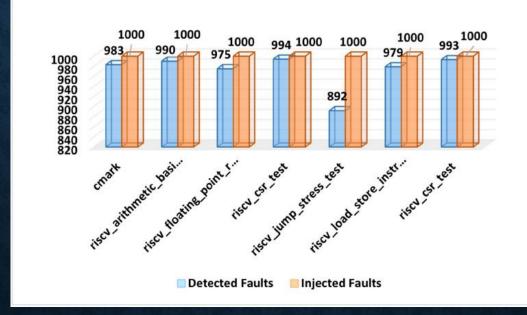

#### RESULTS

- Approximately 20,000 errors are injected by FI campaigns.

- The DCLS feature successfully detects 98.7% of errors from the overall fault injection routines.

- The application cases and their number of detected versus injected faults are shown below

## **FUTURE DIRECTIONS**

- Add new Fault-Injection scenarios

- Use advanced AI features to model the faults

- Test the enhanced fault-injection framework with different cores architectures

## FVDCLS: Functional Verification of RISCV based Dual-Core Lockstep Feature using Fault Injection Mechanism

Muhammad Kashif Minhas, Haroon Waris, and Sajid Baloch Centers of Excellence in Science & Applied Technologies, Pakistan kashifminhas934@gmail.com, haroonwaris@gmail.com, to\_baloch@hotmail.com

## **FVDCLS RESEARCH PAPER**

Research paper accepted in VLSI-SoC Conference Morocco, 2024

## **INTRODUCTION TO RISC-V ISA**

- RISC-V (pronounced "risk-five"): An open-source implementation of a reduced instruction set computing (RISC) based instruction set architecture (ISA)

- Permitting any person or group to construct compatible computers

- Originated in 2010 by researchers at UC Berkeley

- RISC-V ISA includes: A small base integer ISA, usable by itself as a base for customized accelerators or for educational purposes, and

- ✓ Optional standard extensions, to support general-purpose software development

- ✓ Optional customer extensions

### **INTRODUCTION TO RISC-V ISA**

- ISA support is given by RV + word-width + extensions supported permitting any person or group to construct compatible computers

- ✓ *RV32I means 32-bit RISC-V with support for the I(Integer) instruction set*

- A mandatory Base integer ISA I: Integer instructions

- Standard Extensions

- M: Integer Multiplication and Division

A: Atomic Instructions

F: Single-Precision Floating-Point

D: Double-Precision Floating-Point

C: Compressed Instructions (16 bit)

| XLEN-1 |            | 0 |

|--------|------------|---|

|        | x0 / zero  |   |

|        | x1         |   |

|        | x2         |   |

|        | x3         |   |

|        | x4         |   |

|        | <b>x</b> 5 |   |

|        | x6         |   |

|        | x7         |   |

|        | x8         |   |

|        | x9         |   |

|        | x10        |   |

|        | x11        |   |

|        | x12        |   |

|        | x13        |   |

|        | x14        |   |

|        | x15        |   |

|        | x16        |   |

|        | x17        |   |

|        | x18        |   |

|        | x19        |   |

|        | x20        |   |

|        | x21        |   |

|        | x22        |   |

|        | x23        |   |

|        | x24        |   |

|        | x25        |   |

|        | x26        |   |

|        | x27        |   |

|        | x28        |   |

|        | x29        |   |

|        | x30        |   |

|        | x31        |   |

|        | XLEN       |   |

| XLEN-1 |            | 0 |

|        | pc         |   |

|        | XLEN       |   |

#### RV32/64 PROCESSOR REGISTER SET

• 32 32/64-bit integer registers (x0-x31)

x0 always contains a 0

• 32 floating-point (FP) registers (f0-f31)

Each can contain a single- or double-precision FP value (32-bit or 64-bit IEEE FP)

• Program counter (pc) which holds the address of the current instruction

#### **DIFFERENT RISC-V INSTRUCTIONS**

| Category      | Instruction                | Example           | Meaning                   | Comments                                   |

|---------------|----------------------------|-------------------|---------------------------|--------------------------------------------|

|               | Add                        | add x5, x6, x7    | x5 = x6 + x7              | Three register operands; add               |

| Arithmetic    | Subtract                   | sub x5, x6, x7    | x5 = x6 - x7              | Three register operands; subtract          |

| Arithmetic    | Add immediate              | addi x5, x6, 20   | x5 = x6 + 20              | Used to add constants                      |

|               | Load word                  | lw x5, 40(x6)     | x5 = Memory[x6 + 40]      | Word from memory to register               |

|               | Load word, unsigned        | lwu x5, 40(x6)    | x5 = Memory[x6 + 40]      | Unsigned word from memory to register      |

|               | Store word                 | sw x5, 40(x6)     | Memory[x6 + 40] = x5      | Word from register to memory               |

|               | Load halfword              | lh x5, 40(x6)     | x5 = Memory[x6 + 40]      | Halfword from memory to register           |

| Data transfer | Load halfword,<br>unsigned | lhu x5, 40(x6)    | x5 = Memory[x6 + 40]      | Unsigned halfword from memory to register  |

|               | Store halfword             | sh x5, 40(x6)     | Memory[x6 + 40] = x5      | Halfword from register to memory           |

|               | Load byte                  | lb x5, 40(x6)     | x5 = Memory[x6 + 40]      | Byte from memory to register               |

|               | Load byte, unsigned        | lbu x5, 40(x6)    | x5 = Memory[x6 + 40]      | Byte unsigned from memory to register      |

|               | Store byte                 | sb x5, 40(x6)     | Memory[x6 + 40] = x5      | Byte from register to memory               |

|               | Load reserved              | lr.d x5, (x6)     | x5 = Memory[x6]           | Load; 1st half of atomic swap              |

|               | Store conditional          | sc.d x7, x5, (x6) | Memory[x6] = x5; x7 = 0/1 | Store; 2nd half of atomic swap             |

|               | Load upper<br>immediate    | lui x5, 0x12345   | x5 = 0x12345000           | Loads 20-bit constant shifted left 12 bits |

|               | And                        | and x5, x6, x7    | x5 = x6 & x7              | Three reg. operands; bit-by-bit AND        |

|               | Inclusive or               | or x5, x6, x8     | x5 = x6   x8              | Three reg. operands; bit-by-bit OR         |

| Logical       | Exclusive or               | xor x5, x6, x9    | $x5 = x6 ^ x9$            | Three reg. operands; bit-by-bit XOR        |

| Logical       | And immediate              | andi x5, x6, 20   | x5 = x6 & 20              | Bit-by-bit AND reg. with constant          |

#### **DIFFERENT RISC-V INSTRUCTIONS**

| Category      | Instruction                          | Example          | Meaning                    | Comments                                                   |

|---------------|--------------------------------------|------------------|----------------------------|------------------------------------------------------------|

|               | Shift left logical                   | sll x5, x6, x7   | x5 = x6 << x7              | Shift left by register                                     |

|               | Shift right logical                  | srl x5, x6, x7   | $x5 = x6 \gg x7$           | Shift right by register                                    |

|               | Shift right arithmetic               | sra x5, x6, x7   | $x5 = x6 \gg x7$           | Arithmetic shift right by register                         |

| Shift         | Shift left logical<br>immediate      | slli x5, x6, 3   | x5 = x6 << 3               | Shift left by immediate                                    |

|               | Shift right logical<br>immediate     | srli x5, x6, 3   | x5 = x6 >> 3               | Shift right by immediate                                   |

|               | Shift right arithmetic<br>immediate  | srai x5, x6, 3   | x5 = x6 >> 3               | Arithmetic shift right by immediate                        |

|               | Branch if equal                      | beq x5, x6, 100  | if (x5 == x6) go to PC+100 | PC-relative branch if registers equal                      |

|               | Branch if not equal                  | bne x5, x6, 100  | if (x5 != x6) go to PC+100 | PC-relative branch if registers not equal                  |

|               | Branch if less than                  | blt x5, x6, 100  | if (x5 < x6) go to PC+100  | PC-relative branch if registers less                       |

| Conditional   | Branch if greater or equal           | bge x5, x6, 100  | if (x5 >= x6) go to PC+100 | PC-relative branch if registers greater<br>or equal        |

| branch        | Branch if less, unsigned             | bltu x5, x6, 100 | if (x5 < x6) go to PC+100  | PC-relative branch if registers less, unsigned             |

|               | Branch if greater or equal, unsigned | bgeu x5, x6, 100 | if (x5 >= x6) go to PC+100 | PC-relative branch if registers greater or equal, unsigned |

| Unconditional | Jump and link                        | jal x1, 100      | x1 = PC+4; go to PC+100    | PC-relative procedure call                                 |

| branch        | Jump and link register               | jalr x1, 100(x5) | x1 = PC+4; go to $x5+100$  | Procedure return; indirect call                            |

#### **RISC-V GREEN CARD**

| Base                                    | e Integer          | Inst     | ructio | ons: RV      | 32I, RI         | /64I, and RV.                            | 64I, and RV128I |      |          | RV Privileged Instructions |                        |         |           |       |

|-----------------------------------------|--------------------|----------|--------|--------------|-----------------|------------------------------------------|-----------------|------|----------|----------------------------|------------------------|---------|-----------|-------|

| Category                                | Name               |          |        | RV32I Ba     |                 | +RV{64                                   |                 |      | Categor  |                            | Name                   |         | V mnem    | onic  |

| Loads                                   | Load Byte          | Ι        | LB     | rd,rs1       | ,imm            |                                          |                 |      | CSR Acc  | cess /                     | Atomic R/W             | CSRRW   | rd,csr    | ,rs1  |

| Lo                                      | ad Halfword        | I        | LH     | rd,rs1       | ,imm            |                                          |                 |      | A        | tomic Rea                  | ad & Set Bit           | CSRRS   | rd,csr    | ,rs1  |

|                                         | Load Word          | I        | LW     | rd,rs1       | ,imm            | $L{D Q}$ rd                              | ,rs1,i          | imm  | Ato      | mic Read                   | & Clear Bit            | CSRRC   | rd,csr    | rs1,  |

| Load By                                 | te Unsigned        | I        | LBU    | rd,rs1       | ,imm            |                                          |                 |      |          | Atom                       | ic R/W Imm             | CSRRWI  | rd,csr    | ,imm  |

| Load H                                  | alf Unsigned       | I        | LHU    | rd,rs1       | , imm           | L{W D}U rd                               | ,rs1,i          | imm  | Atomic   | Read &                     | Set Bit Imm            | CSRRSI  | rd,csr    | ,imm  |

| Stores                                  | Store Byte         | S        | SB     | rs1,rs       | 2,imm           |                                          |                 |      | Atomic R | ead & Cl                   | ear Bit Imm            | CSRRCI  | rd,csr    | ,imm  |

| Sto                                     | re Halfword        | S        | SH     | rs1,rs       | 2,imm           |                                          |                 |      | Change   | Level                      | Env. Call              | ECALL   |           |       |

|                                         | Store Word         | S        | SW     | rs1,rs       | 2,imm           | S{D Q} rs                                | 1,rs2,          | ,imm | Envi     | ronment                    | Breakpoint             | EBREAK  |           |       |

| Shifts                                  | Shift Left         | R        | SLL    | rd,rs1       | rs2             | SLL{W D} rd                              | ,rs1,1          | rs2  |          | Environr                   | nent Return            | ERET    |           |       |

|                                         | t Immediate        | I        | SLLI   | rd,rs1       |                 | SLLI{W D} rd                             |                 |      | Trap Re  |                            |                        |         |           |       |

| onne Eor                                | Shift Right        |          | SRL    | rd,rs1       | -               |                                          | ,rs1,1          |      | -        |                            | Hypervisor             |         |           |       |

| Shift Righ                              | t Immediate        | I        | SRLI   | rd,rs1       |                 | SRLI{W D} rd                             |                 |      |          |                            |                        |         |           |       |

| -                                       | t Arithmetic       | R        | SRA    | rd,rs1       |                 |                                          | ,rs1,1          |      |          |                            | for Interrupt          |         |           |       |

|                                         | t Arith Imm        | I        | SRAI   | rd,rs1       |                 | SRAI{W D} rd                             |                 |      | MMU      |                            | visor FENCE            |         | .VM rs1   |       |

| Arithmeti                               |                    | R        | ADD    | rd,rs1       |                 |                                          | ,rs1,1          |      | <u> </u> | Caper                      |                        | 21 2000 |           |       |

|                                         | ) Immediate        | I        | ADDI   | rd,rs1       |                 | ADDI{W D} rd                             |                 |      |          |                            |                        |         |           |       |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | SUBtract           | R        | SUB    | rd,rs1       |                 | SUB{W D} rd                              |                 |      |          |                            |                        |         |           |       |

| Land                                    |                    | U        | LUI    | rd,imm       | /102            | le l |                 |      | cod (16  | bit) T                     | nstruction             | n Exto  | ncionul   |       |

|                                         | Upper Imm          |          | AUIPC  |              |                 |                                          |                 | Fmt  | Sea (10  | RVC                        | ISLIUCIIO              |         | /I equiva |       |

| Logical                                 | r Imm to PC<br>XOR | R        | XOR    |              |                 |                                          | ame<br>Word     | CL   | C.LW     |                            | 1/                     |         |           |       |

| -                                       |                    |          |        | rd,rs1       |                 |                                          |                 |      |          |                            | 1',imm                 |         | ,rs1',i   |       |

| XO                                      | R Immediate        | I        | XORI   | rd,rs1       |                 | Load Wo                                  |                 | CI   | C.LWSP   | rd,imm                     |                        |         | sp,imm*   |       |

|                                         | OR                 | R        | OR     | rd,rs1       |                 | Load D                                   |                 | CL   | C.LD     |                            | 1′,imm                 |         | ,rs1',i   |       |

| OF                                      | ۲ Immediate        | I        | ORI    | rd,rs1       |                 | Load Dou                                 |                 | CI   | C.LDSP   | rd,imm                     |                        |         | sp,imm*   |       |

|                                         | AND                | R        | AND    | rd,rs1       | ,rs2            | Load                                     | l Quad          | CL   | C.LQ     | rd',rs                     | 1′,imm                 | LQ rd'  | ,rs1',i   | mm*16 |

|                                         | ) Immediate        | I        | ANDI   | rd,rs1       | ,imm            | Load Qu                                  |                 | CI   | C.LQSP   | rd,imm                     | 1.                     |         | sp,imm*   |       |

| Compare                                 | Set <              | R        | SLT    | rd,rs1       | ,rs2            | Stores Store                             | Word            | CS   | C.SW     | rs1′,r                     | s2′,imm                | SW rs1  | ',rs2',   | imm*4 |

| Set <                                   | < Immediate        | I        | SLTI   | rd,rs1       | ,imm            | Store Wo                                 | ord SP          |      | C.SWSP   | rs2,im                     | m                      | SW rs2  | ,sp,imm   | *4    |

| Set                                     | < Unsigned         | R        | SLTU   | rd,rs1       | ,rs2            | Store D                                  | Double          | CS   | C.SD     | rs1′,r                     | s2′,imm                | SD rs1  | ',rs2',   | imm*8 |

| Set < Im                                | ım Unsigned        | I        | SLTIU  | rd,rs1       | ,imm            | Store Dou                                | ble SP          | CSS  | C.SDSP   | rs2,im                     | m                      | SD rs2  | ,sp,imm   | *8    |

| Branches                                | Branch =           | SB       | BEQ    | rs1,rs       | 2,imm           | Store                                    | Quad            | CS   | c.so     | rs1',r                     | s2',imm                | SQ rs1  | ',rs2',   | imm*1 |

|                                         | Branch ≠           | SB       | BNE    | rs1,rs       | 2,imm           | Store Qu                                 | ad SP           | CSS  | C.SQSP   | rs2,im                     | m                      | SQ rs2  | ,sp,imm   | *16   |

|                                         | Branch <           | SB       | BLT    | rs1,rs       | 2,imm           | Arithmetic                               | ADD             | CR   | C.ADD    | rd,                        | rs1                    |         | rd,rd,r   |       |

|                                         | Branch ≥           | SB       | BGE    | rs1,rs       | 2,imm           | ADD                                      | Word            | CR   | C.ADDW   | rd,                        | rs1                    | ADDW    | rd,rd,i   | mm    |

| Branch                                  | < Unsigned         | SB       | BLTU   | rs1,rs       | 2,imm           | ADD Imm                                  | ediate          | CI   | C.ADDI   | rd,                        | imm                    | ADDI    | rd,rd,i   | mm    |

| Branch                                  | ≥ Unsigned         | SB       | BGEU   | rs1,rs       |                 | ADD Word                                 | d Imm           | CI   | C.ADDIW  |                            | imm                    |         | rd,rd,i   |       |

| Jump & Li                               | nk J&L             | UJ       | JAL    | rd,imm       |                 | ADD SP Imn                               | n * 16          | CI   | C.ADDI1  | 6SP x0,                    | imm                    | ADDI    | sp,sp,i   | mm*16 |

| Jump & L                                | ink Register       | τυ       | JALR   | rd,rs1       | ,imm            | ADD SP Im                                | nm * 4          | CIW  | C.ADDI4: | SPN rd'                    | ,imm                   | ADDI    | rd',sp,   | imm*4 |

| Synch S                                 | ynch thread        | I        | FENCE  |              |                 | Load Imm                                 | ediate          | CI   | C.LI     | rd,                        | imm                    | ADDI    | rd,x0,i   | mm    |

| Synch                                   | Instr & Data       | I        | FENCE  | .1           |                 | Load Upper                               | r Imm           | CI   | C.LUI    | rd,                        | imm                    | LUI     | rd,imm    |       |

| System S                                | ystem CALL         | Ι        | SCALL  | i.           |                 | 1                                        | MoVe            | CR   | C.MV     | rd,                        | rs1                    | ADD     | rd,rs1,   | x0    |

| Sy                                      | stem BREAK         | I        | SBREA  | К            |                 |                                          | SUB             | CR   | C.SUB    | rd,                        |                        |         | rd,rd,r   |       |

| Counters                                | ReaD CYCLE         | I        | RDCYC  | LE r         | d               | Shifts Shift Lef                         | ft Imm          | CI   | C.SLLI   |                            | imm                    |         | rd,rd,i   |       |

| ReaD CYCL                               | E upper Half       | I        | RDCYC  | LEH r        | d               | Branches Bran                            | nch=0           | CB   | C.BEQZ   |                            | ',imm                  |         | rs1',x0   |       |

|                                         | ReaD TIME          | I        | RDTIM  | E r          | d               | Bra                                      | nch≠0           | CB   | C.BNEZ   |                            | ,imm                   | ~       | rs1',x0   | -     |

| ReaD TIM                                | E upper Half       | I        | RDTIM  |              |                 | Jump                                     | Jump            | CJ   | C.J      | imm                        | -                      |         | x0,imm    |       |

|                                         | STR RETired        | I        | RDINS  |              |                 | Jump Re                                  | egister         | CR   | C.JR     |                            | rs1                    |         | x0,rs1,   | 0     |

|                                         | R upper Half       | I        |        | TRETH r      |                 | Jump & Link                              |                 | CJ   | C.JAL    | imm                        |                        |         | ra,imm    |       |

|                                         |                    | -        |        |              |                 | Jump & Link Re                           |                 | CR   | C.JALR   | rs1                        |                        |         | ra,rs1,   | 0     |

|                                         |                    |          |        |              |                 | System Env. E                            | -               | CI   | C.EBREAL |                            |                        | EBREAK  |           | -     |

|                                         |                    | 2-64     | Inct-  | uction F     | ormate          | u *                                      |                 |      |          |                            | C) Instance            |         |           |       |

|                                         |                    |          |        |              |                 |                                          |                 | CR   | 15 14 13 | 12 11                      | C) Instruc<br>10 9 8 7 | 6 5     | 4 3 2     | 1 0   |

|                                         | 30 25 24           | 21<br>rs |        | 19 15<br>rs1 | 14 12<br>funct3 |                                          | 0               | CI   | funct    |                            | rd/rs1                 |         | rs2       | op    |

| R fr                                    | nct7               |          |        |              |                 |                                          |                 |      | funct3   | imm                        | rd/rs1                 |         | mm        |       |

funct3

funct3

funct3

funct3

funct3

imm

imm

imm

offset

imm

rs1'

rs1'

rs1'

jump target

offset

imm

imm

rd'

rd'

rs2'

op

op

op

op

op

op

|    | 31 30       | 25      | 24 21    | 20    | 19  | 15 14   | 12 | 11 8     | 1       | 0     | 0 0  | Γ   |

|----|-------------|---------|----------|-------|-----|---------|----|----------|---------|-------|------|-----|

| R  | funct7      |         | rs2      |       | rs1 | funct   | 3  | re       | 1       | opcod |      | - 1 |

| I  |             | imm[11: | :0]      |       | rs1 | funct   | 3  | re       | 1       | opcod | 0    | ss  |

| s  | imm[11:     | 5]      | rs2      |       | rs1 | funct   | 3  | imm      | [4:0]   | opcod | C    | IW  |

| SB | imm[12] imr | n[10:5] | rs2      |       | rs1 | funct   | 3  | imm[4:1] | imm[11] | opcod |      |     |

| υ  |             |         | imm[31:1 | 2]    |     |         |    | re       | 1       | opcod | e C  | 5   |

| נט | imm[20]     | imm[10: | 1] in    | m[11] | imm | [19:12] |    | re       | 1       | opcod | e C  | B∣  |

|    |             |         |          |       |     |         |    |          |         |       | _ C. | յլ  |

#### Free & Open $\mathbb{R} = \mathbb{R} = \mathbb{C} - \mathbb{C}$ Reference Card (riscv.org) (2)

|                   | Loa<br>Sto<br>Swa<br>Add |

|-------------------|--------------------------|

|                   | Log<br>Min               |

| <b>RISC-V</b>     | Cat<br>Mov               |

| <b>GREEN CARD</b> | Con                      |

|           |                              |       | Optional Multiply-Divide                                      | e Instruc  |               |                          |                                  |

|-----------|------------------------------|-------|---------------------------------------------------------------|------------|---------------|--------------------------|----------------------------------|

| Category  | Name                         | Fmt   | RV32M (Multiply-Divide)                                       |            | +RV{6         |                          |                                  |

| Multiply  | MULtiply                     | R     | MUL rd,rs1,rs2                                                | MUL{W D    | } 1           | rd,rs1,rs2               |                                  |

|           | MULtiply upper Half          |       | MULH rd,rs1,rs2                                               |            |               |                          |                                  |

|           | JLtiply Half Sign/Uns        |       | MULHSU rd,rs1,rs2                                             |            |               |                          |                                  |

|           | tiply upper Half Uns         |       | MULHU rd,rs1,rs2                                              | DTV(WID    | , ,           | nd wal wal               |                                  |

| Divide    | DIVide United                | R     | DIV rd,rs1,rs2                                                | DIV{W D    | } 1           | rd,rs1,rs2               |                                  |

| Remainde  | DIVide Unsigned<br>REMainder | R     | DIVU rd,rs1,rs2<br>REM rd,rs1,rs2                             | REM{W D    | , ,           | rd,rs1,rs2               |                                  |

|           | REMainder Unsigned           | R     | REM rd,rs1,rs2<br>REMU rd,rs1,rs2                             |            | -             |                          |                                  |

|           |                              |       |                                                               | REMU { W   | D} 1          | rd,rs1,rs2               |                                  |

| Category  | Name                         | Fmt   | A Atomic Instruction Extensi<br>RV32A (Atomic)                | OII: RVA   | +RV{6-        | 1 1 28]                  |                                  |

| Load      | Load Reserved                | R     | LR.W rd,rs1                                                   | LR.{DQ     | -             | rd,rs1                   |                                  |

| Store     | Store Conditional            | R     | SC.W rd,rs1,rs2                                               | SC.{DQ     |               | rd,rs1,rs2               |                                  |

| Swap      | SWAP                         |       | AMOSWAP.W rd,rs1,rs2                                          | AMOSWAP    | ,             | rd,rs1,rs2               |                                  |

| Add       | ADD                          |       | AMOADD.W rd,rs1,rs2                                           | AMOADD.    |               | rd,rs1,rs2               |                                  |

| Logical   | XOR                          |       | AMOXOR.W rd,rs1,rs2                                           | AMOXOR.    | ( 14)         | rd,rs1,rs2               |                                  |

| _         | AND                          | R     | AMOAND.W rd,rs1,rs2                                           | AMOAND.    |               | rd,rs1,rs2               |                                  |

|           | OR                           | R     | AMOOR.W rd,rs1,rs2                                            | AMOOR. {   | ,             | rd,rs1,rs2               |                                  |

| Min/Max   | MINimum                      | R     | AMOMIN.W rd,rs1,rs2                                           | AMOMIN.    |               | rd,rs1,rs2               |                                  |

|           | MAXimum                      | R     | AMOMAX.W rd,rs1,rs2                                           | AMOMAX.    |               | rd,rs1,rs2               |                                  |

|           | MINimum Unsigned             | R     | AMOMINU.W rd,rs1,rs2                                          |            |               | rd,rs1,rs2               |                                  |

|           | MAXimum Unsigned             | R     | AMOMAXU.W rd,rs1,rs2                                          |            |               | rd,rs1,rs2               |                                  |

| Tł        | hree Optional Fl             | oatii | ng-Point Instruction Extension                                |            |               |                          |                                  |

| Category  | Name                         | Fmt   |                                                               |            | +RV{6         |                          |                                  |

| Move      | Move from Integer            | R     | FMV.{H S}.X rd,rs1                                            | FMV.{D     |               | rd,rs1                   |                                  |

|           | Move to Integer              | R     | FMV.X.{H S} rd,rs1                                            | FMV.X.{    |               | rd,rs1                   |                                  |

| Convert   | Convert from Int             | R     | FCVT.{H S D Q}.W rd,rs1                                       | FCVT. {H   | S D Q}.       | <pre>.{L T} rd,rs1</pre> |                                  |

| Conve     | rt from Int Unsigned         | R     | FCVT.{H S D Q}.WU rd,rs1                                      |            |               | .{L T}U rd,rs1           |                                  |

|           | Convert to Int               | R     | FCVT.W. {H S D Q} rd,rs1                                      |            |               | S D Q} rd,rs1            |                                  |

| Con       | vert to Int Unsigned         | R     | FCVT.WU.{H S D Q} rd,rs1                                      | FCVT.{L    | T}U.{H        | S D Q} rd,rs1            |                                  |

| Load      | Load                         | I     | FL{W,D,Q} rd,rs1,imm                                          |            |               | RISC-V Callin            | ng Convention                    |

| Store     | Store                        | S     | FS{W,D,Q} rs1,rs2,imm                                         | Register   | ABI Nam       |                          | Description                      |

| Arithmeti |                              | R     | FADD.{S D Q} rd,rs1,rs2                                       | x0         | zero          |                          | Hard-wired zero                  |

|           | SUBtract                     | R     | FSUB.{S D Q} rd,rs1,rs2                                       | ×1         | ra            | Caller                   | Return address                   |

|           | MULtiply                     | R     | FMUL.{S D Q} rd,rs1,rs2                                       | x2         | sp            | Callee                   | Stack pointer                    |

|           | DIVide                       |       | FDIV.{S D Q} rd,rs1,rs2                                       | x3         | gp            |                          | Global pointer                   |

| Mul-Add   | SQuare RooT<br>Multiply-ADD  | R     | FSQRT.{S D Q} rd,rs1                                          | x4<br>x5-7 | tp<br>+0-2    | Caller                   | Thread pointer<br>Temporaries    |

|           | Multiply-SUBtract            |       | FMADD.{S D Q} rd,rs1,rs2,rs3                                  |            | t0-2<br>s0/fp | Callee                   | Saved register/frame pointer     |

| Negati    | ve Multiply-SUBtract         | R     | FMSUB.{S D Q} rd,rs1,rs2,rs3<br>FNMSUB.{S D Q} rd,rs1,rs2,rs3 |            | su/ip<br>s1   | Callee                   | Saved register                   |

| -         | gative Multiply-ADD          | R     | FNMADD.{S D Q} rd,rs1,rs2,rs3                                 |            | a0-1          | Caller                   | Function arguments/return values |

| Sign Inje |                              | R     | FSGNJ.{S D Q} rd,rs1,rs2                                      | x12-17     | a0-1<br>a2-7  | Caller                   | Function arguments               |

|           | egative SiGN source          | R     | $FSGNJN.{S D Q} rd,rs1,rs2$                                   | x18-27     | s2-11         | Callee                   | Saved registers                  |

|           | Xor SiGN source              | R     | FSGNJX. $\{S   D   Q\}$ rd,rs1,rs2                            | x28-31     | t3-t6         | Caller                   | Temporaries                      |

| Min/Max   | MINimum                      | R     | FMIN.{SDQ} rd,rs1,rs2                                         | f0-7       | ft0-7         | Caller                   | FP temporaries                   |

| -         | MAXimum                      | R     | FMAX.{S D Q} rd,rs1,rs2                                       | f8-9       | fs0-1         | Callee                   | FP saved registers               |

| Compare   | Compare Float =              | R     | FEQ.{S D Q} rd,rs1,rs2                                        | f10-11     | fa0-1         | Caller                   | FP arguments/return values       |

|           | Compare Float <              | R     | FLT.{S D Q} rd,rs1,rs2                                        | f12-17     | fa2-7         | Caller                   | FP arguments                     |

|           | Compare Float ≤              | R     | FLE.{S D Q} rd,rs1,rs2                                        | f18-27     | fs2-11        | Callee                   | FP saved registers               |

| Categoriz | ation Classify Type          | R     | FCLASS.{S D Q} rd,rs1                                         | f28-31     | ft8-11        | Caller                   | FP temporaries                   |

|           | tion Read Status             | R     | FRCSR rd                                                      |            |               |                          |                                  |

| -         | Read Rounding Mode           | R     | FRRM rd                                                       |            |               |                          |                                  |

|           | Read Flags                   | R     | FRFLAGS rd                                                    |            |               |                          |                                  |

|           | Swap Status Reg              | R     | FSCSR rd,rs1                                                  |            |               |                          |                                  |

| s         | wap Rounding Mode            | R     | FSRM rd,rs1                                                   |            |               |                          |                                  |

|           | Swap Flags                   | R     | FSFLAGS rd,rs1                                                |            |               |                          |                                  |

| Swap F    | Rounding Mode Imm            | I     | FSRMI rd,imm                                                  |            |               |                          |                                  |

|           | Swap Flags Imm               | I     | FSFLAGSI rd,imm                                               |            |               |                          |                                  |

53

#### **RISC-V INSTRUCTION FORMATS**

#### Specification from RISC-V website

✓ https://riscv.org/specifications/

| 31 25   | 24 20                      | ) 19  | 15 14 |          | 12 11         |      | 76     |        | 0  |

|---------|----------------------------|-------|-------|----------|---------------|------|--------|--------|----|

| funct7  | rs2                        | rs1   |       | funct3   |               | rd   |        | opcode |    |

| 7       | 5                          | 5     |       | 3        |               | 5    |        | 7      |    |

| 0000000 | $\operatorname{src2}$      | src1  | AD    | D/SLT/   | SLTU          | dest |        | OP     |    |

| 0000000 | src2                       | src1  | AN    | D/OR/2   | XOR           | dest |        | OP     |    |

| 0000000 | $\operatorname{src2}$      | src1  |       | SLL/SR   | L             | dest |        | OP     |    |

| 0100000 | $\operatorname{src2}$      | src1  |       | SUB/SR   | A             | dest |        | OP     |    |

| 31      |                            | 20 19 |       | 15 14 12 | 11            | 76   |        | 0      |    |

|         | $\operatorname{imm}[11:0]$ |       | rs1   | funct3   | $\mathbf{rd}$ |      | opcode |        |    |

|         | 12                         |       | 5     | 3        | 5             |      | 7      |        |    |

|         | offset[11:0]               |       | base  | width    | dest          |      | LOAD   |        |    |

|         |                            |       |       |          |               |      |        |        |    |

| Sinte a |                            |       |       |          |               |      |        |        |    |

| 31      | 25 24                      | 20 19 |       | 15 14 12 | 11            | 76   |        | 0      |    |

| ir      | nm[11:5]                   | rs2   | rs1   | funct3   | imm[4:(       | )]   | opcode |        | 54 |

|         | 7                          | 5     | 5     | 3        | 5             |      | 7      |        |    |

| 0       | ffset[11:5]                | src   | base  | width    | offset[4:     | 0]   | STORE  |        |    |

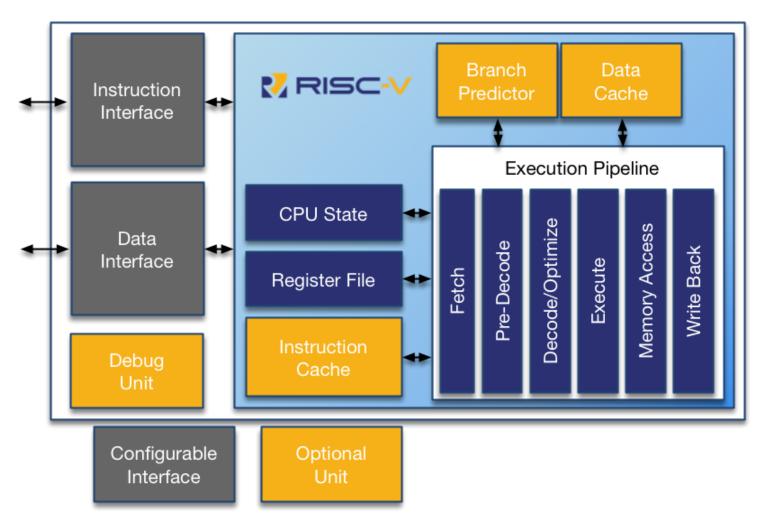

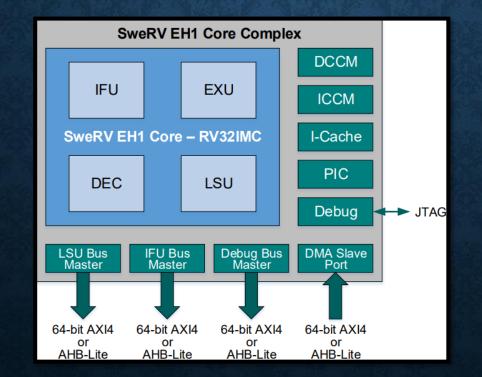

### **DESIGN UNDER VERIFICATION**

- <u>https://github.com/chipsalliance/Cores-SweRV</u>

- The Western Digital SWERV Core EH1 is a 32-bit, dual-issue, 9-stage pipeline core.

- Dual-issue: each clock cycle the processor can move two instructions from one stage of the pipeline to the next stage.

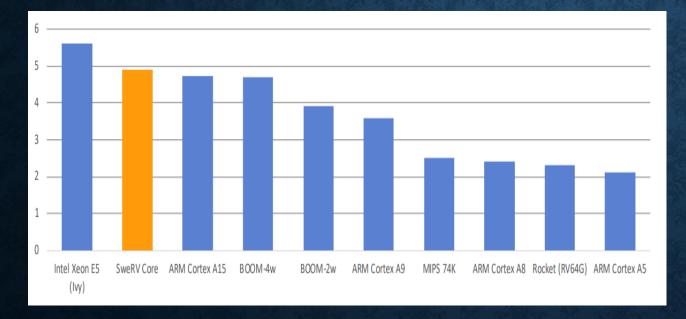

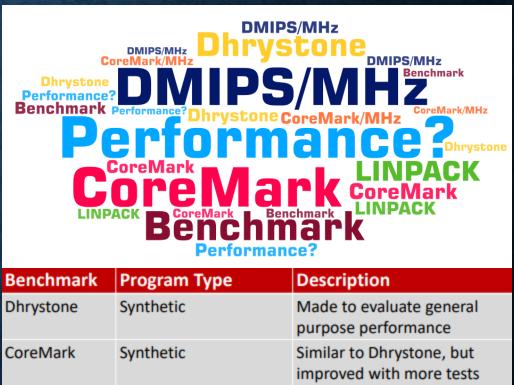

#### **RISC-V PROCESSOR BENCHMARKING**

- Benchmarks determine processor performance by running programs that exercise the hardware.

- This enables comparison of different processors.

4.9 CoreMark/MHz (The CoreMark Score is the number of iterations completed per second)

2.3 DMIPs/MHz (It's a measure of how many operations the CPU can perform in a single clock cycle)

#### MOTIVATION

Accelerate the verification of RISC-V cores by incorporating open-source verification solutions instead of re-inventing the wheel.

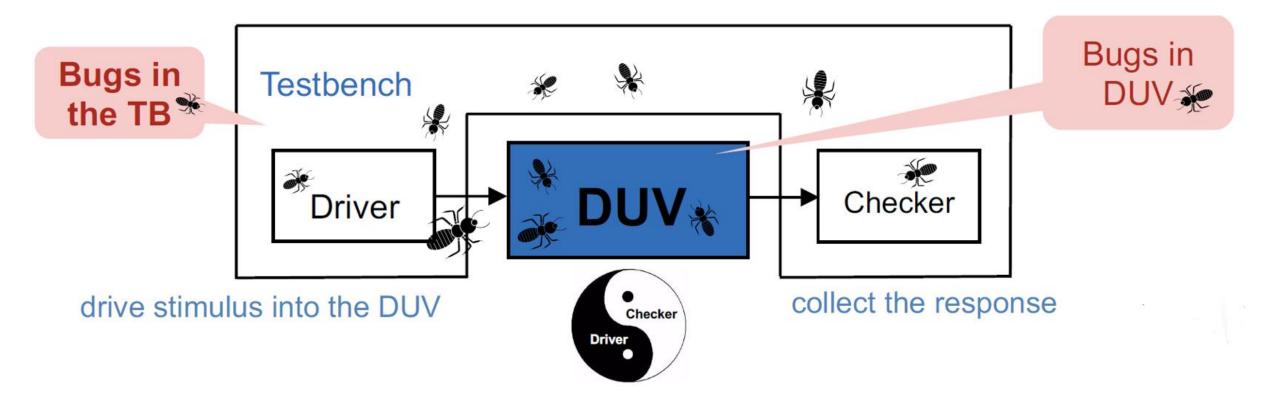

### **BUILDING BLOCKS OF CPU VERIFICATION**

A CPU level design verification environment Includes;

- DUT RTL

- Testbench

- Instantiates RTL

- Driver, Monitor and Scoreboard

- Tests Generator

- Golden Reference Model

Building all these blocks from scratch takes a lot of time and resources

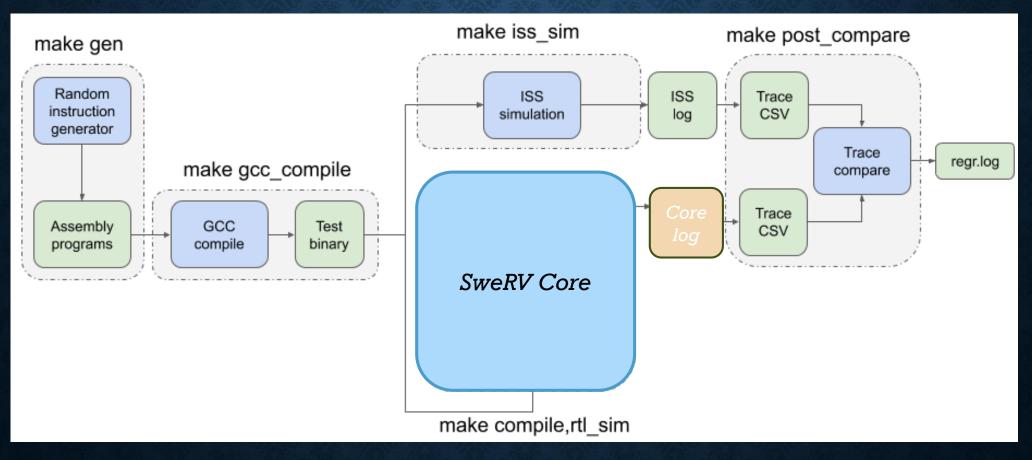

#### **OPEN-SOURCE RISC-V ECOSYSTEM**

#### Google RISC-V DV

- An open-source constraint random instruction Generator for RISC-V processor verification

- Contains Open-source RISC-V Test-Suite

- RISC-V Toolchain

#### Spike ISS

Open-source RISC-V ISA simulator which implements a functional model of RISC-V Core

#### SWERV-EH1

The Western Digital SWERV Core EH-1 is a 32-bit, dual-issue, 9-stage pipeline core

#### SPECIFICATIONS AND SOFTWARE FROM RISCV.ORG AND GITHUB.COM/RISCV

Open-Source RISC-V processor verification framework

https://github.com/Lampro-Mellon/LM-RISCV-DV

RISC-V software includes

GNU Compiler Collection (GCC) toolchain (with GDB, the debugger)

- https://github.com/riscv/riscv-tools

- A simulator ("Spike")

- ✓ https://github.com/riscv/riscv-isa-sim

• A list from

https://github.com/riscvarchive/riscv-cores-list

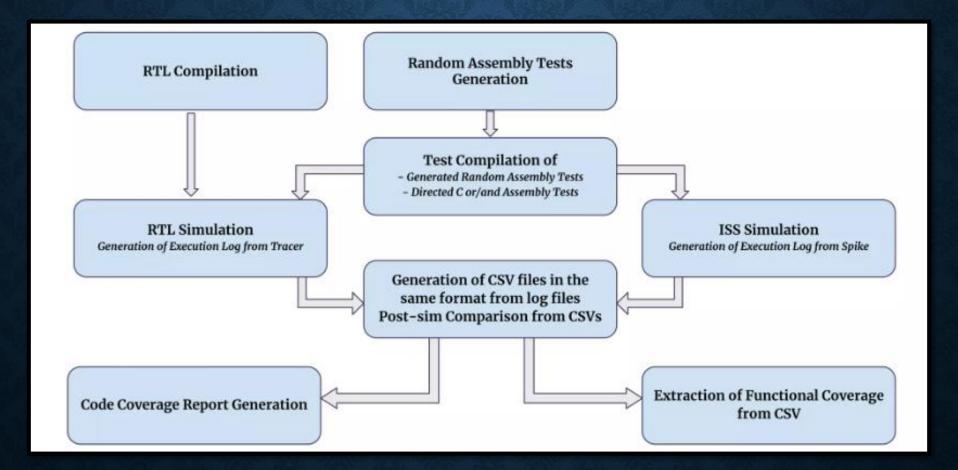

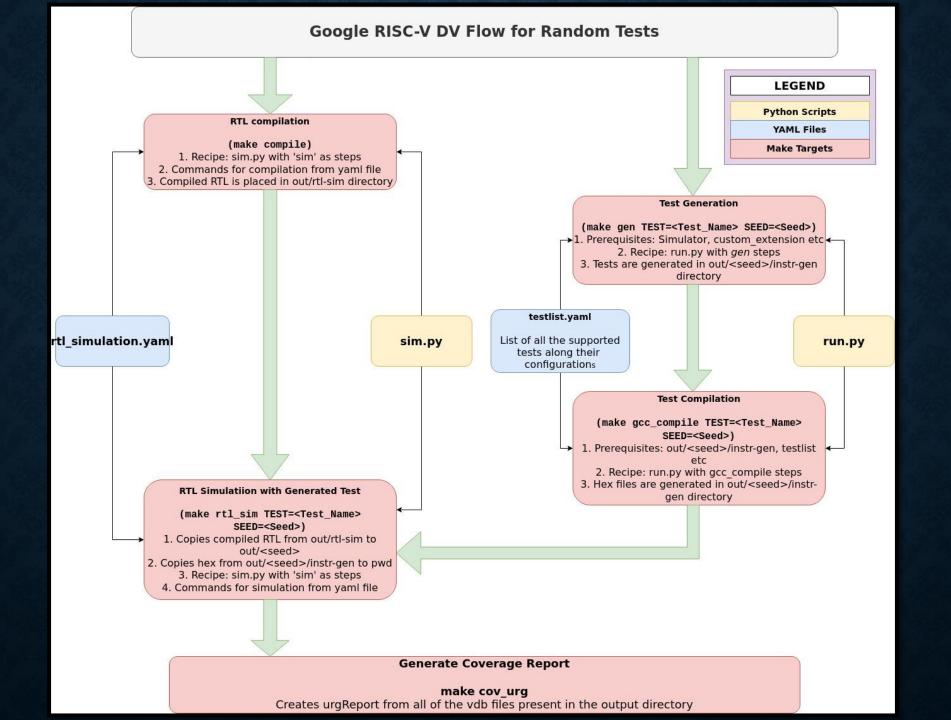

# FLOW DIAGRAM

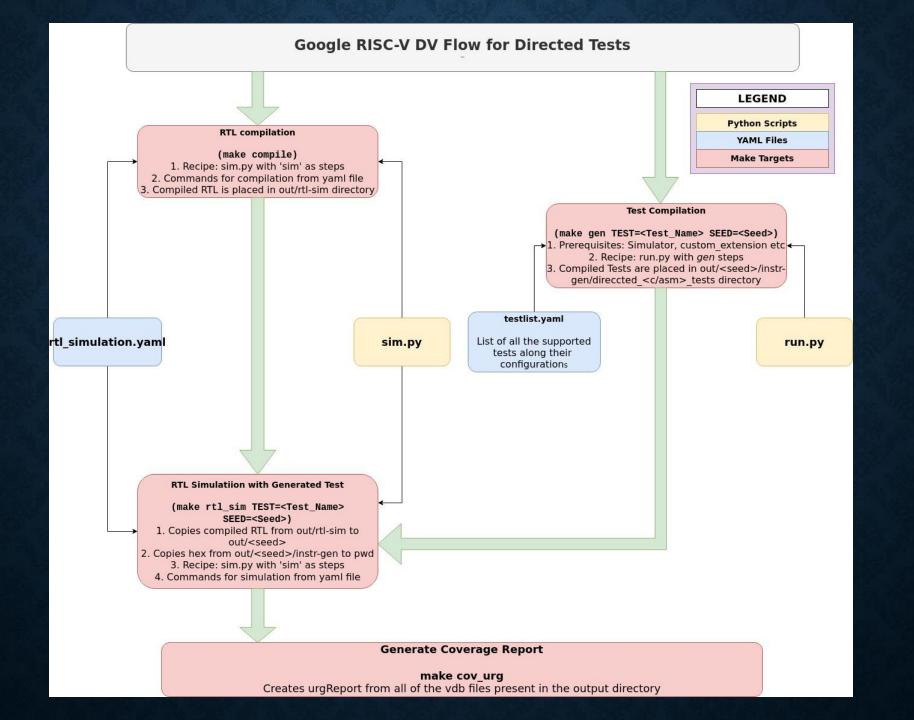

#### **FLOW DIAGRAM**

#### FLOW DIAGRAM WITH COVERAGE

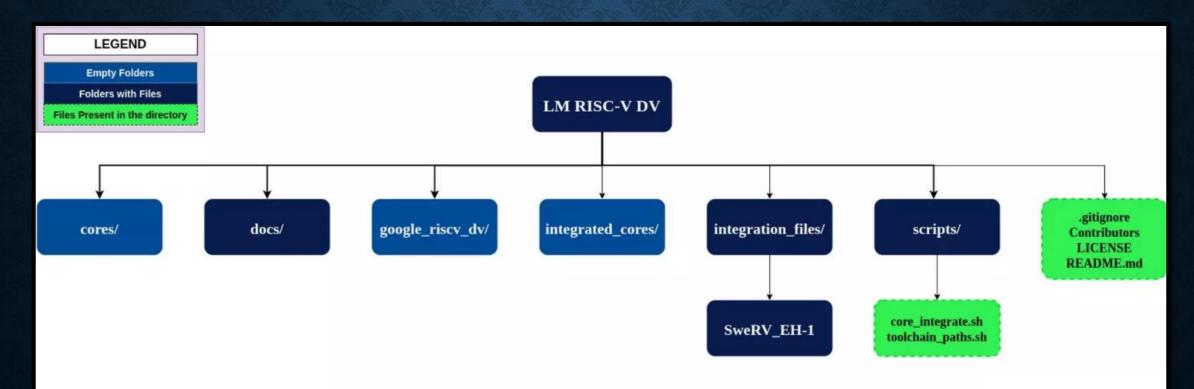

#### **RISC-V DV REPOSITORY**

\* Some files are not shown here for keeping the tree diagram tidy

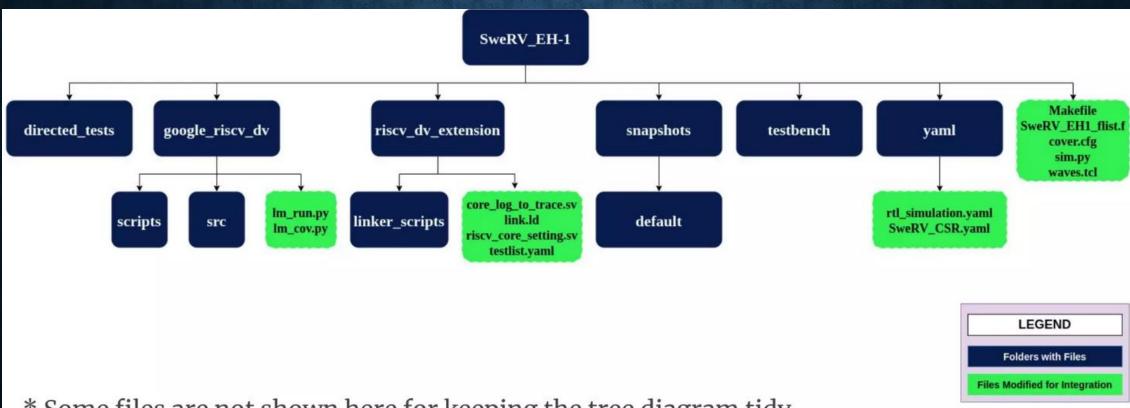

#### FILES FOR INTEGRATION

\* Some files are not shown here for keeping the tree diagram tidy

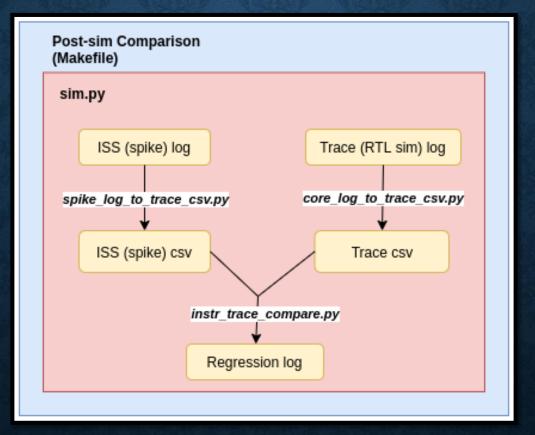

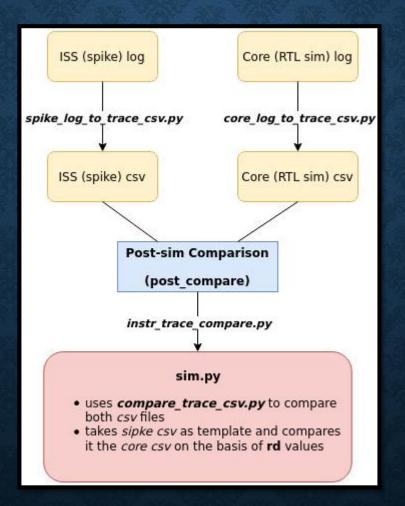

#### **POST-COMPARISON STEPS**

#### **POST-COMPARISON STEPS**

## **INITIAL SETTINGS**

#### **TOOLS SETTINGS**

- Add the VCS compiler into the rtl\_simulation.yaml file and add the flist there.

- SweRV\_flist.f file contains all the files included in the design hierarchy.

- SweRV flist & rtl\_simulation.yaml file is shown in fig:

+incdir+\${PRJ\_DIR}/rtl/lib

+incdir+\${PRJ\_DIR}/rtl/include

+incdir+\${PRJ\_DIR}/snapshots/default

#### +libext+.v

#### // Including Defines Files

\${PRJ\_DIR}/snapshots/default/common\_defines.vh

\${PRJ\_DIR}/rtl/include/swerv\_types.sv

#### // Including Design Files

\${PRJ\_DIR}/rtl/swerv\_wrapper.sv \${PRJ\_DIR}/rtl/mem.sv \${PRJ\_DIR}/rtl/pic\_ctrl.sv \${PRJ\_DIR}/rtl/swerv.sv \${PRJ\_DIR}/rtl/dma\_ctrl.sv \${PRJ\_DIR}/rtl/ifu/ifu\_aln\_ctl.sv \${PRJ\_DIR}/rtl/ifu/ifu\_compress\_ctl.sv \${PRJ\_DIR}/rtl/ifu/ifu\_ifc\_ctl.sv \${PRJ\_DIR}/rtl/ifu/ifu\_ifc\_ctl.sv \${PRJ\_DIR}/rtl/ifu/ifu\_ic\_mem.sv \${PRJ\_DIR}/rtl/ifu/ifu\_ic\_mem.sv \${PRJ\_DIR}/rtl/ifu/ifu\_ic\_mem.sv \${PRJ\_DIR}/rtl/ifu/ifu\_ic\_mem.sv \${PRJ\_DIR}/rtl/ifu/ifu\_ic\_mem.sv \${PRJ\_DIR}/rtl/ifu/ifu\_ic\_mem.sv \${PRJ\_DIR}/rtl/ifu/ifu\_ic\_mem.sv

#### tool: vc compile: cmd: - "vcs -full64 -LDFLAGS '-Wl,--no-as-needed' -assert svaext -sverilog +error+500 <cov opts> -timescale=1ns/10ps -f SweRV\_EH1\_flist.f -Mdir=<out>/vcs simv.csrc -o <out>/vcs simv -l <out>/compile.log -lca -kdb <cmp opts> <wave opts>" wave opts: > -debug access+all -ucli -do waves.tcl cov opts: > -cm line+tgl+branch -cm\_hier cover.cfg -cm dir <out>/test.vdb sim: cmd: > env SIM DIR=<sim dir> <out>/vcs simv +vcs+lic+wait <sim opts> <wave opts> <cov opts> +tracer file base=<sim dir>/trace core -l <sim dir>/sim.log wave opts: > -ucli -do <cwd>/waves.tcl cov opts: > -cm line+tgl+branch -cm\_name test\_<test\_name>\_<iteration> -cm dir <out>/test.vdb tool: verilator compile: cmd: - "verilator --cc -CFLAGS \"-std=c++11\" -Wno-UNOPTFLAT -I/testbench -f flist verilator.f --top-module tb top -exe test tb top.cpp --autoflush --trace -f testbench veri.f" - "cp ./testbench/test tb top.cpp obj dir" - "make -C obj dir -f Vtb top.mk OPT FAST=\"-02\"" sim: cmd: > ./obj\_dir/Vtb\_top +dumpon >><sim\_dir>/sim.log env SIM DIR=<sim dir>

<sim\_opts>

l <sim dirs/sim loo

+tracer\_file\_base=<sim\_dir>/trace\_core

#### **RISC-V CORE SETTINGS**

Configure the riscv\_core\_setting.sv file according to SweRV core parameters e.g, mode, supported ISA etc.

// Parameter for SATP mode, set to BARE if address translation is not supported

parameter satp\_mode\_t SATP\_MODE = BARE;

// Supported Privileged mode privileged\_mode\_t supported\_privileged\_mode[] = {MACHINE\_MODE};

// Unsupported instructions

riscv\_instr\_name\_t unsupported\_instr[];

// ISA supported by the processor riscv\_instr\_group\_t supported\_isa[\$] = {RV32I, RV32M, RV32C};

//To do (): Add RV32C after fixing post compare for RV32C

// Interrupt mode support

mtvec\_mode\_t supported\_interrupt\_mode[\$] = {DIRECT, VECTORED};

// The number of interrupt vectors to be generated, only used if VECTORED interrupt mode is

// supported

int max\_interrupt\_vector\_num = 16;

// Physical memory protection support

bit support\_pmp = 0;

// Debug mode support

bit support\_debug\_mode = 0;

// Support delegate trap to user mode

bit support\_umode\_trap = 0;

// Support sfence.vma instruction

bit support\_sfence = 0;

// Support unaligned load/store

bit support\_unaligned\_load\_store = 1'b1;

// GPR setting

parameter int NUM\_FLOAT\_GPR = 32;

parameter int NUM\_GPR = 32;

parameter int NUM\_VEC\_GPR = 32;

// // Vector extension configuration | Not implemented in SweRV-EH1 //

// Parameter for vector extension

parameter int VECTOR\_EXTENSION\_ENABLE = 0;

### STANDARD RISC-V SweRV CSRs CONFIGURATIONS

- Configure all the SweRV core CSRs with bit fields in the SweRV\_CSR.yaml file.

- Screenshot of the SweRV mstatus & mie CSRs is shown in fig:

MSTATUS csr: mstatus description: > Machine status address: 0x300 privilege mode: M rv32: - field name: mie description: > M-mode interrupt enable type: WARL reset val: 0 msb: 3 lsb: 3 - field name: mpie description: > Previous value of interrupt-enable bit type: WARL reset val: 0 msb: 7 lsb: 7 - field name: mpp0 desription : > Previous privilege mode type: R reset\_val: 0x1 msb: 11 lsb: 11 - field name: mpp1 desription : > Previous privilege mode type: R reset\_val: 0x1 msb: 12 lsb: 12 field name: mprv description: > Modify Privilege (Loads and stores use MPP for privilege checking) type: R reset val: 0 msb: 17 lsb: 17 MIE csr: mie description: > Contains interrupt information address: 0x304 privilege mode: M rv32: field name: msie description: > M-mode software interrupts enable type: WARL reset val: 0 msb: 3 lsb: 3 - field name: mtie description: > M-mode timer interrupt enable type: WARL reset val: 0 msb: lsb: 7 - field name: meie

#### **TESTS INCLUSION**

- Tests to be run (Directed/Random) on core should be present in "testlist.yaml" file. Parameters like instruction count & iterations are set in this file.

- Screenshot of "riscv\_arithmetic\_basic\_test" is shown below:

- test: riscv\_arithmetic\_basic\_test description: > Arithmetic instruction test, no load/store/branch instructions gen\_opts: > +instr\_cnt=2000 +num\_of\_sub\_program=0 +directed\_instr\_0=riscv\_int\_numeric\_corner\_stream,4 +no\_fence=1 +no\_data\_page=1 +no\_branch\_jump=1 +boot\_mode=m +no\_csr\_instr=1 iterations: 2 gen\_test: riscv\_instr\_base\_test rtl test: core base test

# TESTS COMPILATION & GENERATION

```

Top Level Modules:

tb top

TimeScale is 1 ns / 10 ps

VCS Coverage Metrics Release S-2021.09-SP2-1_Full64 Copyright (c) 1991-2021 by Synopsys Inc.

Starting vcs inline pass...

42 modules and θ UDP read.

recompiling package swerv types

recompiling module mem

recompiling module pic ctrl

recompiling module cmp and mux

recompiling module ifu aln ctl

recompiling module ifu compress ctl

recompiling module ifu ifc ctl

recompiling module ifu bp ctl

recompiling module ifu

recompiling module dec dec ctl

recompiling module dec gpr ctl

recompiling module dec tlu ctl

recompiling module dec timer ctl

recompiling module dec trigger

recompiling module dec

recompiling module exu alu ctl

recompiling module exu div ctl

recompiling module exu

recompiling module lsu

recompiling module lsu clkdomain

recompiling module lsu lsc ctl

recompiling module lsu bus intf

recompiling module lsu ecc

recompiling module lsu dccm ctl

recompiling module lsu trigger

recompiling module dbg

recompiling module dmi wrapper

recompiling package pkg

recompiling package tracer pkg

recompiling module tracer

recompiling module tb top

recompiling module rvoclkhdr

recompiling module rybradder

recompiling module rvtwoscomp

recompiling module rvmaskandmatch

recompiling module rvbtb tag hash

recompiling module rvbtb addr hash

recompiling module rvbtb ghr hash

recompiling module rvrangecheck

recompiling module rveven paritygen

recompiling module rvecc encode

recompiling module rvecc decode

All of 42 modules done

make[1]: Entering directory '/home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/integrated cores/SweRV EH1/out/rtl sim/vcs sim

rm -f cuarc*.so csrc*.so pre vcsobj *.so share vcsobj *.so

if [ -x /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/integrated cores/SweRV EH1/out/rtl sim/vcs simv \

]; then chmod a-x /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/integrated cores/SweRV EH1/out/rtl sim/vcs simv; \

g++ -o /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/integrated cores/SweRV EH1/out/rtl sim/vcs simv \

-Wl,--no-as-needed -rdynamic -Wl,-rpath='$ORIGIN'/vcs simv.daidir -Wl,-rpath=./vcs simv.daidir \

-Wl,-rpath=/home/ubuntu/Synopsys installed/vcs/vcs/S-2021.09-SP2-1/linux64/lib -L/home/ubuntu/Synopsys installed/vcs/vcs/S-2021.09-SP2-1/linux64/li

-Wl,-rpath-link=./ -Wl,--no-as-needed objs/amcQw d.o 2903 archive 1.so SIM l.o \

rmapats mop.o rmapats.o rmar.o rmar nd.o rmar llvm 0 1.o rmar llvm 0 0.o

-lvirsim -lerrorinf -lsnpsmalloc -lvfs -lvcsnew -lsimprofile -lreader_common /home/ubuntu/Synopsys_installed/vcs/vcs/S-2021.09-SP2-1/linux64/li

-luclinative /home/ubuntu/Synopsys installed/vcs/vcs/S-2021.09-SP2-1/linux64/lib/vcs tls.o \

-Wl,-whole-archive -lvcsucli -Wl,-no-whole-archive

./../vcs simv.daidir/vc hdrs.o \

/home/ubuntu/Synopsys installed/vcs/vcs/S-2021.09-SP2-1/linux64/lib/vcs save restore new.o \

-ldl -lc -lm -lpthread -ldl

/home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/integrated cores/SweRV EH1/out/rtl sim/vcs simv \

up to date

make[1]: Leaving directory '/home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/integrated cores/SweRV EH1/out/rtl sim/vcs simv

CPU time: 11.989 seconds to compile + .359 seconds to elab + .160 seconds to link

```

Verdi KDB elaboration done and the database successfully generated: 0 error(s), 0 warning(s)

## COMPILING THE TESTBENCH FRAMEWORK

• Framework Compilation Command:

• "make compile"

Screenshot of *compile\_log* is shown in fig:

#### RISC-V ARITHMETIC BASIC TEST GENERATION

- RISC-V test generation Command:

- "make gen TEST=riscv\_arithmetic\_basic\_test SEED=1"

- Screenshot of test\_generation\_log is shown in fig:

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering LW UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1\_Original\_TB For Reference/google\_riscv\_dv/src/isa/riscv\_instr.sv(101) @ 0: reporter [riscv\_instr] Registering LBU UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering LHU UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering SB UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscy dv/src/isa/riscy instr.sv(101) @ 0: reporter [riscy instr] Registering SH UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering SW UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering SLL UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscy dv/src/isa/riscy instr.sv(101) @ 0: reporter [riscy instr] Registering SLLI UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering SRL UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering SRLI UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering SRA UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering SRAI UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering ADD UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering ADDI UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering NOP UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering SUB UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering LUI UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering AUIPC UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering XOR UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering XORI UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering OR UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscy dv/src/isa/riscy instr.sv(101) @ 0: reporter [riscy instr] Registering ORI UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering AND UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscy dv/src/isa/riscy instr.sv(101) @ 0: reporter [riscy instr] Registering ANDI UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering SLT UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering SLTI UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering SLTU UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering SLTIU UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscy dv/src/isa/riscy instr.sv(101) @ 0: reporter [riscy instr] Registering BEO UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering BNE UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering BLT UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering BGE UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering BLTU UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering BGEU UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering JAL UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering JALR UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscy dy/src/isa/riscy instr.sv(101) @ 0: reporter [riscy instr] Registering FENCE UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/isa/riscv instr.sv(101) @ 0: reporter [riscv instr] Registering FENCE I

#### RISCV ARITHMETIC BASIC TESTGENERATION

- RISC-V test generation Command:

- "make gen TEST=riscv\_arithmetic\_basic\_test SEED=1"

- Screenshot of test\_generation\_log is shown in fig:

```

UVM_INFO /home/ubuntu/SweRV for training/LM_SweRV-EH1 Original_TB_For_Reference/google_riscv_dv/src/riscv_asm_program_gen.sv(1655) @ 0: reporter [asm_gen] Adding directed instruction stream:riscv_int_numeric_corner_stream ratio:4/1006

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/test/riscv instr base test.sv(92) @ 0: uvm test top [uvm test top] All directed instruction is applied

UVM_INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/riscv asm program gen.sv(825) @ 0: reporter [asm gen] Generating privileged mode routing for MACHINE_MODE

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/riscv privileged common seq.sv(97) @ 0: reporter@@privil seq [privil seq] mstatus val: 0x1800

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/riscv asm program gen.sv(1711) @ 0: reporter [asm gen] Insert directed instr stream riscv int numeric corner stream 1/50 times

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/riscv instr sequence.sv(77) @ 0: reporter@@main [main] Start generating 50 instruction

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/riscv instr sequence.sv(87) @ 0: reporter@@main [main] Finishing instruction generation

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/riscv asm program gen.sv(357) @ 0: reporter [asm gen] Randomizing call stack..done

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/riscv asm program gen.sv(121) @ 0: reporter [asm gen] Generating callstack...done

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/riscv asm program gen.sv(123) @ 0: reporter [asm gen] Post-processing main program...done

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/riscv instr sequence.sv(326) @ 0: reporter@@main [main] Injecting 0 illegal instructions, ratio 0/100

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/riscv instr sequence.sv(339) @ 0: reporter@@main [main] Injecting 0 HINT instructions, ratio 0/100

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/riscv asm program gen.sv(125) @ 0: reporter [asm gen] Generating main program instruction stream...done

UVM_INFO /home/ubuntu/SweRV_for_training/LM_SweRV-EH1_Original_TB_For_Reference/google_riscv_dv/src/riscv_asm_program_gen.sv(190) @ 0: reporter [asm_gen] Inserting sub-programs...done

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/riscv asm program gen.sv(191) @ 0: reporter [asm gen] Main/sub program generation...done

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/src/riscv asm program gen.sv(1572) @ 0: reporter [asm gen] out/seed-1/instr gen/asm tests/riscv arithmetic basic test 0.S is generated

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/test/riscv instr base test.sv(70) @ 0: uvm test top [] TEST PASSED

UVM INFO /home/ubuntu/SweRV for training/LM SweRV-EH1 Original TB For Reference/google riscv dv/test/riscv instr base test.sv(74) @ 0: uvm test top [] TEST GENERATION DON

UVM INFO /home/ubuntu/Synopsys installed/vcs/vcs/S-2021.09-SP2-1//etc/uvm-1.2/base/uvm report server.svh(904) @ 0: reporter [UVM/REPORT/SERVER]

--- UVM Report Summary ---

** Report counts by severity

UVM INFO : 531

UVM WARNING : 0

UVM ERROR : 0

UVM FATAL : 0

** Report counts by id

2

[RNTST]

1

[UVM/RELNOTES]

[asm gen]

10

[cfg]

2

[main]

4

[pmp cfg]

2

[privil seq]

[riscv instr]

497

[uvm test top]

4

[vector cfg]

7

$finish called from file "/home/ubuntu/Synopsys installed/vcs/vcs/S-2021.09-SP2-1//etc/uvm-1.2/base/uvm root.svh", line 527.

finish at simulation time

Θ

VCS Simulation Report

```

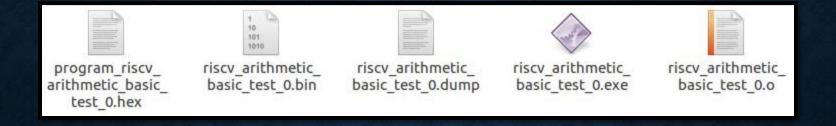

#### RISC-V GENERATED ASSEMBLY TEST

- Generates RISC-V test in the form of assembly code with the file named "riscv\_arithmetic\_basic\_test\_0.S".

- Screenshot of generated test file is shown in fig:

```

1.include "user define.h

2#define STDOUT 0xd0580000

3.globl _start

4.section .text

5 start:

6

.include "user init.s"

csrr x5, 0xf14

7

li x6, 0

8

9

beq x5, x6, 0f

10

110: la x21, h0 start

12 jalr x0, x21, 0

13 h0 start:

li x10, 0x40001104

14

csrw 0x301, x10

15

16 kernel sp:

17

la x12, kernel stack end

18

19 trap_vec_init:

20

la x10, mtvec_handler

21

ori x10, x10, 0

22

csrw 0x305, x10 # MTVEC

23

24 mepc_setup:

la x10, init

25

26

csrw 0x341, x10

27

28 custom csr setup:

29

nop

30